����

����ͼ���������㷺��Ӧ������Ϣ����������θ�Ч�����ؽ���ʵ����ͼ�����ֻ�����Ϣ�����Ĺؼ�����֮һ�����Ļ���FPGA���������һ�����ٶ�·��Ƶ���ݲɼ�ϵͳ������Altera Cyclone IIоƬ������һ������NiosII���˴��������洢����I��O�ӿڡ��Զ�������Ŀɱ��Ƭ��ϵͳϵͳ(System On Programmable Chip��SOPC)������FPGA���ٲ��д�����������ͬʱ�Զ�·��Ƶ���ݽ�����Ƶ���룬������ϵͳ���ݲɼ�ǰ�˵Ĵ���������

SOPCϵͳ�ǿɱ��Ƭ��ϵͳ���ɵ���оƬ�������ϵͳ����Ҫ�����ܣ�ͬʱ�������Ŀ��ع����ԡ��ɸ���ʵ��Ӧ���еIJ�ͬ����ü������䡢����ϵͳ��������Ӳ��ϵͳ���ɱ�̡�NiosII����CPU���������������������ã���������������ٶȿ���ص㡣

1ϵͳ���ܼ��ص�

1��1 ��������

�����������ϵͳ��Altera��˾CycloneIIϵ�е�EP2C70Ϊ���ģ�ͨ�������չ�������Ƶ�źţ���ͬʱ�ɼ�����2��6·��Ƶ���ݣ�����Ƶ���ݽ������ȡ��ͼ�������RAW DATA��SOPCϵͳͨ���Զ���FIFO�ӿڻ������ݣ�����DMA��������Ƶ���ݰ������洢��������������á�

1��2 ϵͳ�ص�

��ϵͳ��Ҫ���������ص㣺

�ٲ���Ӳ���������Ա�д����Ƶ����ģ����Ը�Ч�������Ƶ����빤��������������Ƶ�źű����ʽ��ͬ����������ع�ÿ·��Ƶ�Ľ���ģ�飬������Ҫ��Ӳ����ơ�\

��NiosII����CPU�������ؽ���������ȣ����Nios IDE������̻��������Է���Ķ���ƵA��D�ɼ�оƬ����I2C�������á�

���Զ���FIFO�ӿڻ�����Ƶ���ݣ���֤���������Ժ�ȷ�ԣ�FIFO�Ļ������ij��Ⱥ����ݿ��Ⱦ����Զ��ƣ����ÿһ·��Ƶ���ݸ�ʽ���ò�ͬ��FIFO��������

�ܲ���DMA������ɲɼ����ݴ�SOPC���赽�ڴ�İ��ƣ�����CPU�ĸ�����

2 ʵ��ԭ����ϵͳ�ṹ

2��1 ϵͳ������

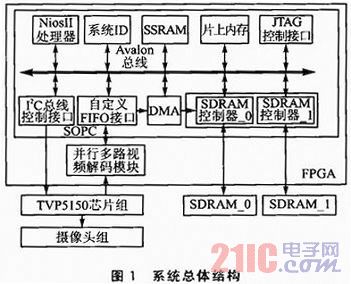

����ϵͳ��Ҫ��ΪSOPCϵͳ����·��Ƶ����ģ�顢��ƵA��DоƬ�SDRAM�洢������ģ�顣SOPCϵͳ�Ͷ�·��Ƶ����ģ�����FPGA�ɱ������Դʵ�֡�SOPCϵͳͨ���Զ���FIFO(Custom FIFO)�������Զ�·��Ƶ����ģ��(Multi-channel Video Decoder Module)�����ݣ�DMA������ݴ�Custom FIFO��SDRAM�İ��ƹ�����NiosII CPUͨ��Avalon���߶���ƵA��D�ɼ�оƬ���Զ���FIFO�ӿ�ģ���Լ�DMA�������������á�ϵͳ����ṹ��ͼ1��ʾ��

����SOPCϵͳ��NiosII������Ϊ���ģ�ͨ��AvaIon������Ϊ�����źź����ݴ������࣬NiosII����CPU�����������������Avalon�����ϣ�����SOPCϵͳ�а���NiosII��������SSRAM��Ƭ���ڴ桢JTAG���ƽӿڡ�I2C���߿��ƽӿڡ��Զ���FIFO�ӿڡ�2��SDRAM��������DMA�ȡ�

2��2 ��Ƶ����ģ�����

��Ƶ�ɼ���չ����TVP5150������ƵA��DоƬΪ���ģ��ɼ�ģ������ͷ�źţ���A��D���������������8λITU-RBT��656��Ƶ�����ʽ��������ͼ��ֱ���Ϊ720x 480������ʱ��Ϊ27 MHz��

��Ƶ����ģ������������ܣ�

�ٸ���ITU-RBT��656���нӿڹ���TVP5150оƬ�����������ת����YUV422��ͼ��RAW DATA��

�ڶ���Ƶ�ֱ��ʽ��е���������Ϊ640×480�ķֱ��ʣ�������Ϊ��Ч��������ʱ����������Ч�źţ������Զ���FIFO��д�����źš�

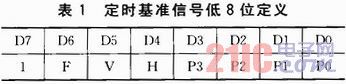

ITU-RBT��656Э���й涨���ź�����Ҫ��3�ࣺ��Ч��Ƶ���������źš���Ƶ��ʱ���źš������źš���Ƶ����ģ���һ��������ؼ�����ο��ټ��ITU-RBT��656��Ƶ����������Ƶ��ʱ���ź�SAV��EAV����ʱ���ź���4���ֽڵ�������ɣ����ʽΪFF0000XY��ǰ3���ֽ�FF0000Ϊ��־���У����һ���ֽ�XY��ʾ�ö�ʱ���ź�ǰ���������λ����������֡��λ�ü��ö�ʱ���ź����͡����һ�ֽ�XYÿһλ�ĺ������1���С�

F��V��H�DZ�־λ��ȡֵ��Ϊ0��1��Fλ��ʶͼ���������泡���ݻ���ż�����ݣ�Vλ��ʶ��ǰ�����Ƿ�Ϊ��Ч���ݣ�Hλ��ʶ�ö�ʱ���ź�ΪSAV����EAV��F��V��H��־λ��ȡֵ�뺬�����2���С����е���λP3��P0���ɸ�4λ����������ã�����F��V��HֵУ��;����롣 P3��P0�Ķ���Ϊ��P3=VH��P2=FH��P1=FV��P0=FVH��

��ͳ���м��ͨ��ʹ��״̬����ʵ�֡�����ƴ��µ�ʹ�û������������ټ�ⶨʱ���źţ�������Ƴ���ṹ�������ںܴ�̶��ϼ����˴�����������ITU-RBT��656Э���ж�ʱ���źŵĶ��壬��������SAV=(Window==24’hFF0000)��(iData[4]==1’b0)������Window����24λ�Ĵ�����iData[7��0]��8λ�����źţ�����ֻȡ��4λ������������ʱÿ������8λ����8λ�������źŲ��롣

����ģ��ĵڶ��������ڵ����ֱ��ʵ�ʱ������Skip�źţ���Skip�ź���Чʱ�������ص����������������ͨ������������Skip�źţ��������ؼ����������ֵ��Ϊ�������ķ��ӣ���ĸΪ9��skip�ź��ɳ������������ƣ�������Ϊ0ʱSkip�ź���Ч���������ַ����������ص���720ת��Ϊ640��

2��3 SOPC�Զ���FIFO�ӿ�

������Ƶ���벿�ֹ�����27 MHz��ʱ��Ƶ���£���NiosII����CPUΪ�˻�ȡ�ϸߵ�ϵͳ��������������SOPCϵͳ������100 MHz��ʱ��Ƶ���¡����ݴ��ⲿ����SOPCϵͳ�Ĺ���������ʱ�ӵIJ�ƥ�䣬������������ظ���ʧ�����첽FIFO���ǽ���������Ĺؼ��������첽FI FO��Ϊ���ݻ���ӿڣ�����ʱ�������������Ƶ����ģ���Raw Dataͼ�����ݣ����дFIFO����������ʱ������ӦDMA�������Ķ�������DMA��������ɶ�FIFO������

��·��Ƶ���ݴ洢�ӿ�ģ��ͨ��SOPC���Զ�������ʵ�֣��������Զ�·��Ƶ���ݲɼ����ɸ���ÿ·��Ƶ���ݵIJ�ͬ��ʽ����Ϊÿ·��Ƶ���ݶ��ƴ洢�ӿڡ��������һ���潵����ϵͳӲ���ṹ�ĸ��Ӷȣ���һ���汣֤ÿ·���ݶ������д��䣬������ݲɼ���Ч�ʡ��Զ�������ӿ���ѭAvalon����Э�飬���ݷ������ݲ����ķ�ʽ��ͬ����ΪMaster��Slave���֣���ϵͳ�Ķ�·���ݴ洢�ӿ�ģ�����Salveģʽ��

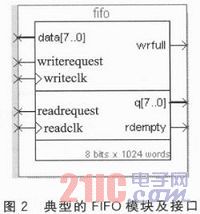

�Զ���洢�ӿ�ģ����FIFO IP CoreΪ���ģ�ͨ����Avalon����Э��ƥ�䣬����NiosII�������Ŀ����źš���ģ������QuartusII��Mega Wizard Plug-In Managerʵ����FIFO IP Core���������ݸ�ʽ��ϵͳ��Դ�ۺϿ��ǣ�FIFO�����ݿ���Ϊ8λ��FIFO���Ϊ1024�������ﱣ��FI FO IP Core�Ķ�ʱ���ź�readclk���������ź�readrequest��8λ��ȡ���ݽӿ�q[7��0]��8λд�����ݽӿ� data[7��0]��дʱ���ź�writec lk��д�����ź�writerequest�Լ�FIFO��״̬�ź�rdempty��ʵ�������FIFOģ����ͼ2��ʾ��

������SOPC�Զ������������ù����У�����������Ҫʵ�ֵĹ��ܣ�FIFO��д���ӦΪSOPCϵͳ�Ķ���ӿڣ�FIFO�Ķ�ȡ��Ӧ��Avalon���߹ҽӣ����ܱ�DMA����ģ���ȡ��ͼ3Ϊʵ������FIFOģ����Ϊ�Զ�����������SOPCϵͳʱ�Ľӿ����á�

2��4 DMA������ģ��

DMA�����������Զ���FIFO�ӿ��е����ݰ������洢����ÿ·��Ƶ����Դ��Ӧһ��FIFO�ӿڣ�ÿ��FIFO�ӿ�����һ��DMAͨ������·��Ƶ���ݵĽ��롢�洢����Ӱ�졣SOPCϵͳ��֧�ֵ�DMA������IP Core����ģʽ��3�֣�

�ٴ洢�����洢��ģʽ�������������Ҫͬʱ����ͨ���ͽ���ͨ��������Դ��ַ��Ŀ���ַ����������

�ڴ洢��������ģʽ�����������ֻҪ����ͨ��������Դ��ַ������Ŀ���ַ�̶���

�����赽�洢��ģʽ�����������ֻҪ����ͨ��������Դ��ַ�̶���Ŀ���ַ������

��ϵͳ����У�DMA���������������ǽ��Զ�������洢�ӿڵ����ݰ�����SDRAM�ڴ��У����Բ��õ�3��DMA����������ģʽ���������赽�洢��ģʽ�����ֹ���ģʽ�£�Դ��ַ���Զ�������ĵ�ַ����һ���̶���ַ����Ŀ���ַ��SDRAM�洢����ַ����Ҫ��ַ�����������ݴ�������У���DMA�������Զ����Ŀ���ַ����������SOPCϵͳ�е�DMA������IP Core�����е�DMA�Ĵ����Ŀ��ȴ�С��������һ��DMA�������ܴ������������С�������������Ƶ�������Ϊһ֡ͼ���С��

2��5 �洢�ռ����

��ϵͳ�����и��ݿ��������Դ������·�ɼ�����Ƶ���ݷֱ�洢������SDRAM�У�SOPCϵͳ������SDRAM�Ļ���ַ�ֱ�ΪSDRAM_0_BASE��SDRAM_1_BASE��һ��SDRAM�д洢��ÿ·��Ƶ���ݼ��RAM_PROTECT_SPACE�ĵ�ַ�ռ䣬DATA_SPACE������ÿ·��Ƶ���ݴ洢��SDRAM�е�Ԥ���ռ��С���ɴ˿ɵõ�n·��Ƶ������SDRAM�еĴ洢�ռ�ĵ�ַ��

��ʼ��ַ��DATA_n_START_Addr=BASE_ADDRESS+RAM_PROTECT_SPACE��

������ַ��DATA_n_END_Addr=DATA_n_START_addr+DATA_SPACE��

3 ϵͳ�������

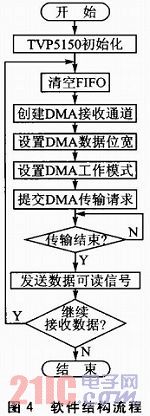

����������������ҪΪTVP5150оƬ��ʼ����DMA�����������õȡ������ṹ������ͼ4��ʾ��

4 ʵ����

Ϊ������ٶ�·��Ƶ���ݲɼ�ϵͳ��ͼ��ɼ�Ч����ϵͳ���4·����ͷͬʱ�ɼ�ͼ�����ݣ���ʵ����Ƶ���ݲɼ������У���·��Ƶͼ����ʾ�������������洢��SDRAM�е�ͼ�����ݶ�ȡ��ͨ�������ں��㷨���ںϳɻ���ƽ��ͼ��ʵ�ʶ�·ͼ��ɼ��ں�Ч����ͼ5��ʾ��

����

���Ļ���FPGA�����һ�ָ��ٶ�·��Ƶ���ݲɼ�ϵͳ����ϵͳͨ�������Ƶ��չ�����Ӷ����Ƶ����ͷ��ͨ����FPGA�ڲ�������Ƶ����ģ�飬�ܹ���ÿ·��Ƶ���ݲ��н��룬���Ҫ��ʵʱ�ԵĶ�·���ݲɼ���Ч�ʣ������ڲ�����Ӳ����Ƶ�ǰ���¶Ա����ʽ�����ݲ��ò�ͬ�Ľ���ģ�顣SOPCϵͳ���Զ���FIFO�ӿ��ܹ����ٻ�����Ƶ���ݡ�ͨ��DMA IP Core��ʹ�ã��ɼ���Niosll����CPU��ȡ����I��O�ӿ�������ռ�õ�ʱ�����ڣ��������ϵͳ�Ĺ���Ч�ʡ�