引言

数字图像处理技术广泛地应用在信息处理领域,如何高效、灵活地将现实世界图像数字化是信息处理的关键技术之一。本文基于FPGA技术设计了一个高速多路视频数据采集系统。基于Altera Cyclone II芯片,构建一个集成NiosII软核处理器、存储器、I/O接口、自定义外设的可编程片上系统系统(System On Programmable Chip,SOPC)。利用FPGA高速并行处理能力,可同时对多路视频数据进行视频解码,大大提高系统数据采集前端的处理能力。

SOPC系统是可编程片上系统,由单个芯片完成整个系统的主要逻辑功能,同时具有灵活的可重构特性。可根据实际应用中的不同需求裁剪、扩充、升级系统,并且软硬件系统均可编程。NiosII软核CPU的外设可由设计者自由配置,具有灵活且运行速度快的特点。

1系统功能及特点

1.1 功能描述

本文所提出的系统以Altera公司CycloneII系列的EP2C70为核心,通过外接扩展板接入视频信号,可同时采集处理2~6路视频数据,将视频数据解码后提取出图像区域的RAW DATA。SOPC系统通过自定义FIFO接口缓存数据,利用DMA技术将视频数据搬移至存储区域,供后续程序调用。

1.2 系统特点

本系统主要具有以下特点:

①采用硬件描述语言编写的视频解码模块可以高效地完成视频编解码工作,如果接入的视频信号编码格式不同,可以灵活重构每路视频的解码模块,而不需要修改硬件设计。\

②NiosII软核CPU可以灵活地进行任务调度,配合Nios IDE软件编程环境,可以方便的对视频A/D采集芯片进行I2C总线配置。

③自定义FIFO接口缓存视频数据,保证数据连贯性和准确性,FIFO的缓冲区的长度和数据宽度均可以定制,针对每一路视频数据格式配置不同的FIFO缓冲区。

④采用DMA技术完成采集数据从SOPC外设到内存的搬移,减轻CPU的负担。

2 实现原理及系统结构

2.1 系统总体框架

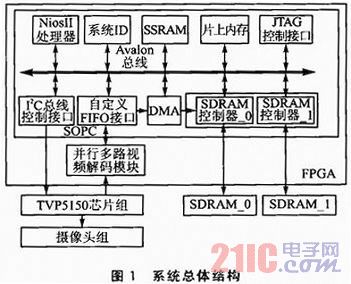

整个系统主要分为SOPC系统、多路视频解码模块、视频A/D芯片绢、SDRAM存储器几大模块。SOPC系统和多路视频解码模块均由FPGA可编程逻辑资源实现。SOPC系统通过自定义FIFO(Custom FIFO)缓冲来自多路视频解码模块(Multi-channel Video Decoder Module)的数据,DMA完成数据从Custom FIFO到SDRAM的搬移工作,NiosII CPU通过Avalon总线对视频A/D采集芯片、自定义FIFO接口模块以及DMA控制器进行配置。系统总体结构如图1所示。

SOPC系统以NiosII处理器为核心,通过AvaIon总线作为控制信号和数据传输中枢,NiosII软核CPU及各类外设均挂载在Avalon总线上,本文SOPC系统中包括NiosII处理器、SSRAM、片上内存、JTAG控制接口、I2C总线控制接口、自定义FIFO接口、2个SDRAM控制器、DMA等。

2.2 视频解码模块设计

视频采集扩展板以TVP5150低功耗视频A/D芯片为核心,采集模拟摄像头信号,经A/D采样后量化编码成8位ITU-RBT.656视频编码格式输出,输出图像分辨率为720x 480,像素时钟为27 MHz。

视频解码模块具有两个功能:

①根据ITU-RBT.656并行接口规则,将TVP5150芯片输出的数据流转换成YUV422的图像RAW DATA。

②对视频分辨率进行调整,调整为640×480的分辨率,当数据为有效区域像素时发出数据有效信号,即对自定义FIFO的写请求信号。

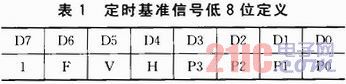

ITU-RBT.656协议中规定的信号中主要有3类:有效视频区域数据信号、视频定时基准信号、辅助信号。视频解码模块第一部分任务关键是如何快速检测ITU-RBT.656视频数据流中视频定时基准信号SAV/EAV。定时基准信号由4个字节的序列组成,其格式为FF0000XY,前3个字节FF0000为标志序列,最后一个字节XY表示该定时基准信号前后的数据行位于整个数据帧的位置及该定时基准信号类型。最后一字节XY每一位的含义如表1所列。

F、V、H是标志位,取值可为0或1。F位标识图像数据是奇场数据还是偶场数据,V位标识当前数据是否为有效数据,H位标识该定时基准信号为SAV还是EAV。F、V、H标志位的取值与含义如表2所列。其中低四位P3~P0是由高4位经异或运算获得,用于F,V和H值校验和纠错码。 P3~P0的定义为:P3=VH,P2=FH,P1=FV,P0=FVH。

传统序列检测通常使用状态机来实现。本设计创新的使用滑动窗法来快速检测定时基准信号,这种设计程序结构清晰,在很大程度上减少了代码量。根据ITU-RBT.656协议中定时基准信号的定义,声明变量SAV=(Window==24’hFF0000)&(iData[4]==1’b0)。其中Window声明24位寄存器,iData[7:0]是8位输入信号,这里只取第4位。滑动窗更新时每次左移8位,低8位用输入信号补齐。

解码模块的第二个功能在调整分辨率的时候引入Skip信号,当Skip信号有效时,该像素点数据跳过。本设计通过除法器控制Skip信号,将行像素计算器的输出值作为除法器的分子,分母为9,skip信号由除法器余数控制,当余数为0时Skip信号有效。采用这种方案将行像素点由720转换为640。

2.3 SOPC自定义FIFO接口

由于视频输入部分工作在27 MHz的时钟频率下,而NiosII软核CPU为了获取较高的系统处理能力,整个SOPC系统工作在100 MHz的时钟频率下。数据从外部进入SOPC系统的过程中由于时钟的不匹配,极易造成数据重复或丢失,而异步FIFO正是解决这个问题的关键。采用异步FI FO作为数据缓冲接口,低速时钟域接收来自视频解码模块的Raw Data图像数据,完成写FIFO操作;高速时钟域响应DMA控制器的读请求,由DMA控制器完成读FIFO操作。

多路视频数据存储接口模块通过SOPC的自定义外设实现,本设计针对多路视频数据采集,可根据每路视频数据的不同格式单独为每路视频数据定制存储接口。这种设计一方面降低了系统硬件结构的复杂度,另一方面保证每路数据独立并行传输,提高数据采集的效率。自定义外设接口遵循Avalon总线协议,根据发起数据操作的方式不同,分为Master和Slave两种,本系统的多路数据存储接口模块采用Salve模式。

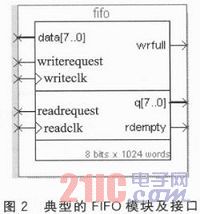

自定义存储接口模块以FIFO IP Core为核心,通过与Avalon总线协议匹配,接收NiosII处理器的控制信号。该模块利用QuartusII中Mega Wizard Plug-In Manager实例化FIFO IP Core,根据数据格式和系统资源综合考虑,FIFO的数据宽度为8位,FIFO深度为1024。在这里保留FI FO IP Core的读时钟信号readclk、读请求信号readrequest、8位读取数据接口q[7:0]、8位写入数据接口 data[7:0]、写时钟信号writec lk、写请求信号writerequest以及FIFO空状态信号rdempty。实例化后的FIFO模块如图2所示。

在SOPC自定义器件的配置过程中,根据我们所要实现的功能,FIFO的写入端应为SOPC系统的对外接口,FIFO的读取端应与Avalon总线挂接,并能被DMA控制模块读取。图3为实例化后FIFO模块作为自定义外设引入SOPC系统时的接口配置。

2.4 DMA控制器模块

DMA控制器负责将自定义FIFO接口中的数据搬移至存储区域,每路视频数据源对应一个FIFO接口,每个FIFO接口配有一个DMA通道,各路视频数据的解码、存储互不影响。SOPC系统所支持的DMA控制器IP Core传输模式有3种:

①存储器到存储器模式。这种情况下需要同时打开发送通道和接收通道,而且源地址和目标地址都是自增。

②存储器到外设模式。这种情况下只要打开发送通道,而且源地址自增,目标地址固定。

③外设到存储器模式。这种情况下只要打开接收通道,而且源地址固定,目标地址自增。

本系统设计中,DMA控制器工作任务是将自定义外设存储接口的数据搬移至SDRAM内存中,所以采用第3种DMA控制器工作模式,即从外设到存储器模式。这种工作模式下,源地址是自定义外设的地址,是一个固定地址。而目标地址是SDRAM存储器地址,需要地址自增,在数据传输过程中,由DMA控制器自动完成目标地址自增操作。SOPC系统中的DMA控制器IP Core配置中的DMA寄存器的宽度大小,决定了一次DMA传输所能传输的数据量大小。本设计所需搬移的数据量为一帧图像大小。

2.5 存储空间设计

本系统方案中根据开发板的资源,将多路采集的视频数据分别存储在两块SDRAM中,SOPC系统中两块SDRAM的基地址分别为SDRAM_0_BASE与SDRAM_1_BASE。一块SDRAM中存储的每路视频数据间隔RAM_PROTECT_SPACE的地址空间,DATA_SPACE定义了每路视频数据存储在SDRAM中的预留空间大小。由此可得第n路视频数据在SDRAM中的存储空间的地址。

起始地址:DATA_n_START_Addr=BASE_ADDRESS+RAM_PROTECT_SPACE。

结束地址:DATA_n_END_Addr=DATA_n_START_addr+DATA_SPACE。

3 系统软件设计

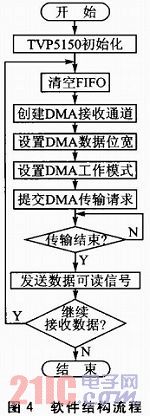

本方案软件部分主要为TVP5150芯片初始化、DMA控制器的配置等。软件结构流程如图4所示。

4 实验结果

为检验高速多路视频数据采集系统的图像采集效果,系统外接4路摄像头同时采集图像数据,在实际视频数据采集过程中,多路视频图像显示连贯流畅。将存储在SDRAM中的图像数据读取后,通过后期融合算法,融合成环境平面图像,实际多路图像采集融合效果如图5所示。

结语

本文基于FPGA设计了一种高速多路视频数据采集系统,该系统通过外接视频扩展板连接多个视频摄像头,通过在FPGA内部构建视频解码模块,能够对每路视频数据并行解码,提高要求实时性的多路数据采集的效率,并可在不更改硬件设计的前提下对编码格式的数据采用不同的解码模块。SOPC系统的自定义FIFO接口能够高速缓存视频数据。通过DMA IP Core的使用,可减少Niosll软核CPU读取低速I/O接口数据所占用的时钟周期,提高整个系统的工作效率。